Description

Hard-Numbers: Technical Specifications

- Processor: Dual-core ARM Cortex-A9 at 667 MHz

- FPGA: Xilinx Zynq-7000 (XC7Z020), 85K logic cells, 220 DSP slices

- System Memory: 512 MB DDR3 RAM, 512 MB NAND flash storage

- Operating System: NI Linux Real-Time (32-bit)

- Integrated Digital I/O: 96 channels (3.3 V LVTTL, ±3 mA max per channel)

- Analog Input (RMC-dependent) : Up to 16 channels, 16-bit, 180 kS/s (with NI 9684 RMC)

- Analog Output (RMC-dependent) : Up to 8 channels, 16-bit, 1 MS/s (with NI 9684 RMC)

- Communication Ports: Gigabit Ethernet (2 ports), CAN (2 ports), RS-232 (1 onboard + 4 via FPGA), RS-485 (2 via FPGA)

- USB: USB 2.0 Hi-Speed (front panel host + RMC host/device)

- RMC Connector: 240-pin high-density connector for C Series modules

- Power Input: 9 to 30 V DC, 28 W maximum with RMC

- Operating Temperature: -40°C to 85°C (-40°F to 185°F)

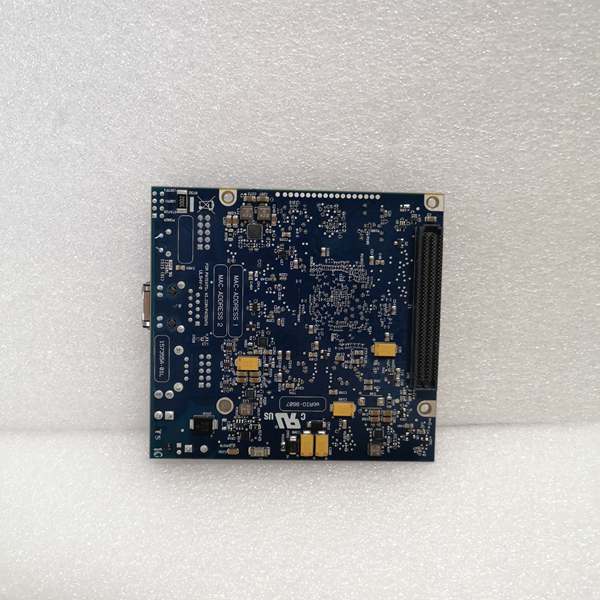

- Dimensions: 70 mm × 45 mm × 8.6 mm (2.76 in. × 1.77 in. × 0.34 in.)

- Weight: 87 g (3.07 oz.)

NI SBRIO-9607

The Real-World Problem It Solves

When you need an embedded controller that fits in tight spaces but still delivers FPGA performance and real-time processing, this single-board package eliminates chassis requirements. The Zynq SoC combines ARM processor and FPGA on one chip, letting you run Linux applications alongside custom hardware logic without the footprint of traditional CompactRIO systems.

Where you’ll typically find it:

- Power inverter controllers for solar, motor drives, and UPS systems

- HIL test rigs for ECU validation where space is at a premium

- OEM embedded systems requiring CAN, Ethernet, and serial I/O in a compact form factor

- Portable test equipment and field-deployed monitoring systems

Bottom line: It packs a full CompactRIO controller into a board the size of a deck of cards, with all the I/O and processing power you need for serious embedded applications.

Hardware Architecture & Under-the-Hood Logic

The sbRIO-9607 centers on a Xilinx Zynq-7000 All Programmable SoC that integrates a dual-core ARM Cortex-A9 processor and FPGA fabric on a single die. NI Linux Real-Time runs on the ARM cores while the FPGA handles user-defined custom logic. An RMC (RIO Mezzanine Card) connector provides expansion to C Series modules for additional analog and digital I/O.

Signal flow and processing logic:

- Power Input: 9-30 V DC input filters and regulates to internal rails (+3.3 V, +5 V, FPGA_VIO).

- ARM Processor: Dual-core Cortex-A9 runs NI Linux Real-Time OS and host applications.

- FPGA Fabric: 85K logic cells execute custom LabVIEW FPGA code for hardware-timed I/O.

- RMC Connector: 240-pin connector routes 96 DIO lines and power to C Series expansion cards.

- Integrated DIO: 96 LVTTL lines connect directly to FPGA for high-speed digital I/O.

- Communication Peripherals: Gigabit Ethernet, CAN, RS-232/485, and USB connect through FPGA fabric.

- DMA Engines: 16 DMA channels transfer data between FPGA memory and ARM DRAM.

- System Memory: 512 MB DDR3 stores applications and data; 512 MB NAND flash provides nonvolatile storage.

NI SBRIO-9607

Field Service Pitfalls: What Rookies Get Wrong

Exceeding RMC Power Limits

The sbRIO-9607 provides +5 V (1.5 A max), +3.3 V_AUX (0.33 A max), and FPGA_VIO (0.33 A max) to the RMC connector. Techs load up RMC cards without checking the total budget, causing brownouts or unpredictable behavior.

- Field Rule: Calculate total RMC power draw before deployment. Sum the requirements of all installed C Series modules and stay under the 28 W system maximum. If you see random reboots under load, measure RMC voltage rails with an oscilloscope.

Overloading DIO Channels

Each digital I/O channel is rated for ±3 mA maximum. New engineers assume FPGA I/O can source/sink like standard 74LVC245 buffers and drive heavy loads, causing signal degradation or FPGA damage.

- Quick Fix: Never connect more than ±3 mA per DIO line. Use external buffers or drivers for relays, LEDs, or other high-current loads. If you’re unsure, measure the sink/source current with a multimeter before connecting to FPGA I/O.

Ignoring RMC Standoff Heights

The RMC connector height combined with mating connector height determines required standoff dimension. Using wrong standoffs causes mechanical stress on the PCB during mating or unmating.

- Field Rule: Calculate standoff height as RMC connector height + mating connector height + 0.15 mm (0.006 in.) minimum clearance. Don’t guess—measure both connectors and verify the total against your mechanical drawings before fabricating mounting hardware.

Losing System Password

The default username is “admin” with no password, but once you set a password, NI cannot recover it. Locked-out controllers require factory reformat which wipes all applications and configuration.

- Field Rule: Document system passwords in your maintenance log immediately after setting them. If you must reset a controller, remember that reformatting is the only option—back up your FPGA bitstreams and Linux applications regularly.

Forgetting CMOS Battery Replacement

The BR1225 coin cell battery maintains RTC when main power is off. Typical life is 2.5 years at 55°C. A dead battery causes time drift on power-up but doesn’t prevent booting.

- Field Rule: Replace the CMOS battery proactively during scheduled maintenance, especially in high-temperature environments. Use only industrial-grade BR1225 or equivalent—consumer CR2032 batteries won’t last in industrial conditions.

Misconfiguring Serial Port Signals

RS-232/485 ports via FPGA DIO require correct CLIP (Component-Level IP) configuration. Wrong bit timing or flow control settings result in garbage data or no communication.

- Field Rule: Use NI sbRIO CLIP Generator to create validated serial port IP. Don’t roll your own UART implementation in LabVIEW FPGA unless you know exactly what you’re doing—serial protocols have strict timing requirements that hand-coded logic often violates.