Description

Key Technical Specifications

-

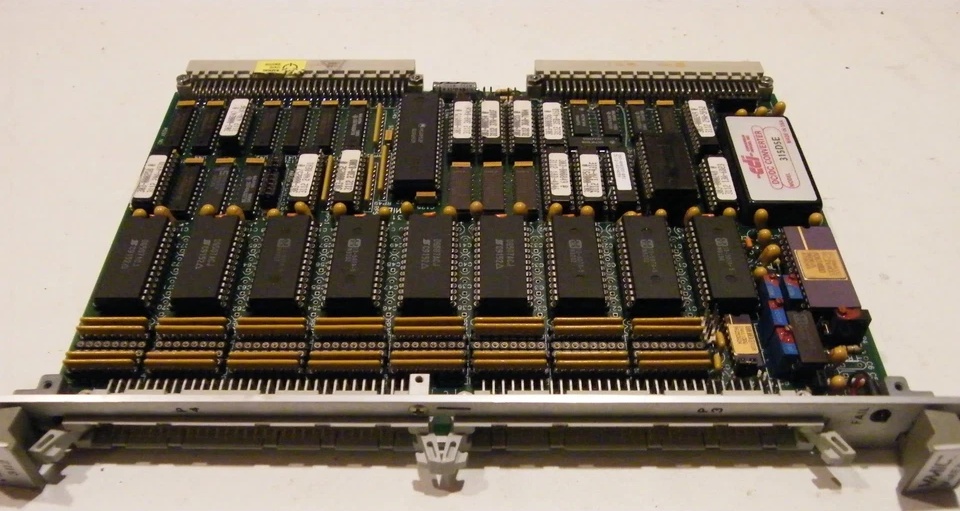

Model Number: VMIVME-3112

-

Manufacturer: GE Fanuc / VMIC (General Electric)

-

Function: 32-channel digital input/output with high-throughput buffering

-

I/O Levels: TTL/CMOS compatible (5 V)

-

Data Path: 32-bit VME slave, DMA-capable

-

Throughput: > 1 MHz per channel (burst)

-

Power: +5 VDC from VME back-plane; no on-board fan required

-

Operating Temperature: 0 °C to +65 °C (no fan)

-

Connectors: Front-panel 50-pin header (screw-terminal or ribbon options)

-

Form Factor: Standard 6U VME64x

-

Status: Factory discontinued – new & tested spares available

Field Application & Problem Solved

In the field the biggest headache is catching high-speed contact changes—valve limit switches, breaker status, or turbine trip inputs—without missing a single edge. The VMIVME-3112 solves that by giving you 32 TTL lines that can be read or written at > 1 MHz. You’ll typically find one per VME crate on Mark-V or Mark-VI retrofits where the CPU needs to see every contact transition in real time. Core value: it collapses 32 isolated digital I/Os, high-speed buffering, and VME DMA into one 6U card you can swap while the turbine is on turning gear

In the field the biggest headache is catching high-speed contact changes—valve limit switches, breaker status, or turbine trip inputs—without missing a single edge. The VMIVME-3112 solves that by giving you 32 TTL lines that can be read or written at > 1 MHz. You’ll typically find one per VME crate on Mark-V or Mark-VI retrofits where the CPU needs to see every contact transition in real time. Core value: it collapses 32 isolated digital I/Os, high-speed buffering, and VME DMA into one 6U card you can swap while the turbine is on turning gear

.

GE VMIVME-3112

Installation & Maintenance Pitfalls (Expert Tips)

TTL Inputs Hate 24 V—Use a Divider

The lines are 5 V TTL; land 24 VDC on a pin and you’ll blow the buffer. Drop a 4.7 kΩ / 1 kΩ divider on the field terminal strip or use the VMIC opto-isolated front-end if you must switch 24 V.

The lines are 5 V TTL; land 24 VDC on a pin and you’ll blow the buffer. Drop a 4.7 kΩ / 1 kΩ divider on the field terminal strip or use the VMIC opto-isolated front-end if you must switch 24 V.

Front-Panel Connector Works Loose

The 50-pin header is held by two screws; if you forget to tighten them vibration walks the plug out and you’ll chase random “I/O fault” alarms. Torque screws to 0.4 Nm and tug-test the cable.

The 50-pin header is held by two screws; if you forget to tighten them vibration walks the plug out and you’ll chase random “I/O fault” alarms. Torque screws to 0.4 Nm and tug-test the cable.

No Fan Means Keep the Crate Clean

The board is rated 0-65 °C with no fan. If your VME crate ingests paper-mill dust the heat-sink fins clog and the buffers start to miss. Blow the crate out every outage or you’ll chase phantom transitions.

The board is rated 0-65 °C with no fan. If your VME crate ingests paper-mill dust the heat-sink fins clog and the buffers start to miss. Blow the crate out every outage or you’ll chase phantom transitions.

Spare Lead-Time Is 6-8 Weeks—Keep One on the Shelf

Factory stock is gone; new & tested spares are available but not overnight. If you crack a buffer or burn a pin you’ll be down until the part arrives—keep one in stores or you’ll discover the weakness during the next grid event

Factory stock is gone; new & tested spares are available but not overnight. If you crack a buffer or burn a pin you’ll be down until the part arrives—keep one in stores or you’ll discover the weakness during the next grid event

.

Technical Deep Dive & Overview

Internally the card is a 32-bit bidirectional buffer bolted to a VME64x slave interface. Each line can be programmed as input or output; the on-board FIFO supports burst DMA so the CPU can read or write all 32 bits in a single bus cycle. No firmware—pure hardware—so you can swap it without reloading parameters; just remember to set the direction register or the lines will float and the CPU will read noise

Internally the card is a 32-bit bidirectional buffer bolted to a VME64x slave interface. Each line can be programmed as input or output; the on-board FIFO supports burst DMA so the CPU can read or write all 32 bits in a single bus cycle. No firmware—pure hardware—so you can swap it without reloading parameters; just remember to set the direction register or the lines will float and the CPU will read noise

.