Description

Hard-Numbers: Technical Specifications

- Bus Interface: PCI Express (PCIe) x1 lane, compatible with x1/x4/x8/x16 slots

- Reflective Memory Capacity: 64 MB to 256 MB (field-upgradable)

- Data Transfer Rate: 174 Mbaud continuous shared memory update

- GPIO Channels: 32 digital channels (sinking/sourcing at 24VDC)

- GPIO Current: 500 mA max per output channel (sourcing)

- Operating Temperature: 0°C to 55°C (32°F to 131°F)

- Isolation Rating: 1500V RMS between GPIO and PCIe bus

- Power Draw: 8W typical from PCIe slot + 500mA @24VDC for GPIO

- Network Nodes: Up to 256 nodes on single reflective memory ring

- Fault Detection: Cyclic Redundancy Check (CRC) on every packet

- Form Factor: Low-profile PCIe card (requires bracket conversion for full-height)

- Firmware: GE VMIC Driver Suite v6.0 or later

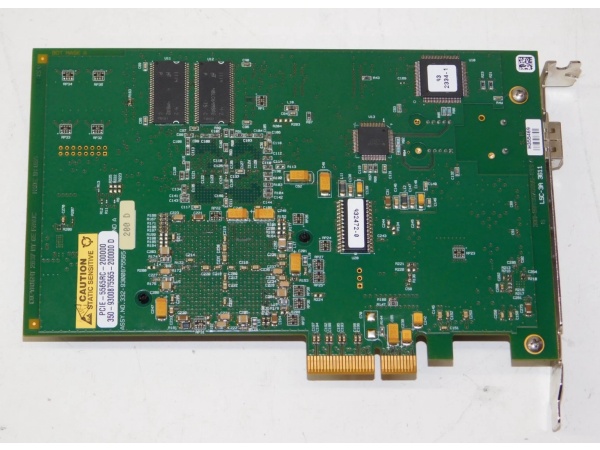

GE PCIE-5565PIORG

The Real-World Problem It Solves

Real-time data sharing between dissimilar control systems introduces latency that’s fatal in applications like turbine control. The PCIE-5565PIORG creates a shared memory space that all network nodes access simultaneously—no network stack, no buffering, no dropped packets. It eliminates race conditions caused by polling-based communication.

Where you’ll typically find it:

- Combined cycle plant power distribution control systems

- Steel mill automation networks requiring real-time sync across PLC nodes

- Offshore oil rig SIS systems needing zero-latency status updates

Bottom line: It’s a hardware fix for inter-system communication latency that software can’t solve.

Hardware Architecture & Under-the-Hood Logic

The module uses a Xilinx FPGA for core processing with no dedicated microprocessor—all network logic runs directly on the FPGA for maximum speed. GPIO channels are optoisolated from the PCIe bus to prevent ground loop currents from corrupting memory transactions.

Signal flow:

- Host writes data to local reflective memory via PCIe bus; FPGA detects the write

- Data is broadcast to all network nodes via fiber optic link at 174 Mbaud

- Other nodes write the updated data to their local memory in lockstep

- GPIO channels are polled every 10ms; state changes update reserved memory addresses

- Shared memory automatically reflects GPIO status to all network nodes

- CRC is calculated on every packet; faults trigger interrupt to host computer

GE PCIE-5565PIORG

Field Service Pitfalls: What Rookies Get Wrong

Forgetting to terminate the reflective memory ringI’ve seen network nodes drop random packets when technicians forget to install termination resistors at both ends of the ring. The open end creates signal reflections that corrupt data.

- Field Rule: Install 120Ω termination resistor at the first and last nodes of the ring. Verify termination with a multimeter while the system is powered down. Replace resistors if they fail continuity tests.

Misapplying GPIO power to the PCIe slotTechnicians often power GPIO directly from the PCIe slot instead of using external 24VDC. This can exceed the slot’s current limit and cause the host computer to crash unexpectedly.

- Field Rule: Power GPIO channels only from external 24VDC supply, never from the PCIe bus. Use a dedicated 24VDC power supply for all digital outputs to avoid brownouts on the PCIe slot.

Overlooking firmware updates after node additionsAfter adding new nodes to the ring, I’ve seen technicians skip firmware updates on older modules. This causes version mismatches and network synchronization failures.

- Field Rule: Update all nodes to the same firmware version after adding new hardware. Use GE’s VMIC Driver Suite to automate updates across the network. Verify synchronization by checking shared memory addresses for consistent values across nodes.

Commercial Availability & Pricing Note

Please note: The listed price is for reference only and is not binding. Final pricing and terms are subject to negotiation based on current market conditions and availability.