Description

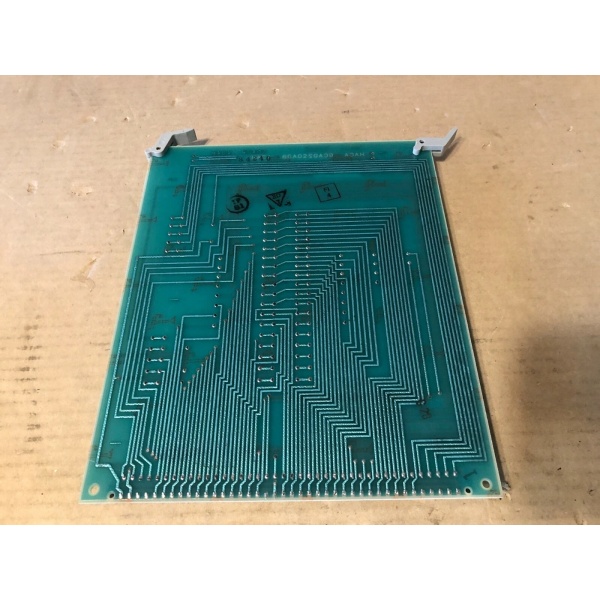

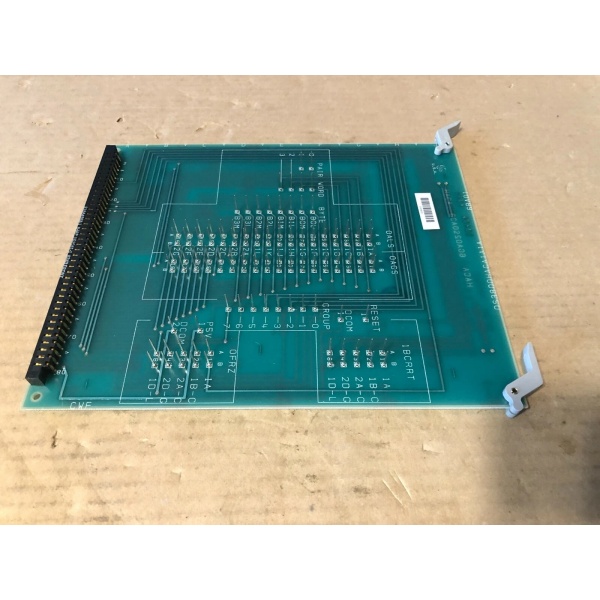

DS3800HACA1A1A: Product Overview

The DS3800HACA1A1A is a daughterboard-grade address decoder that plugs onto a motherboard carrier inside the Mark IV rack. It receives 20-bit address and control lines from the CPU, decodes them into chip-select pulses, and routes them to I/O, memory, or communication daughterboards over the VME back-plane. The card is hardware-configured (no firmware) and deterministic, making it suitable for safety-related address decoding when triple-redundant.

Physical implementation includes TTL decode ICs, opto-isolators, TVS surge suppressors, and 30 gold-pinned jumpers that select memory maps, chip-select enables, and wait-state insertion. 20-pin ribbon connectors (input and output) mate with the carrier motherboard; keyed and gold-plated to prevent mis-insertion or fretting corrosion. Front-edge LEDs (green = decode active, red = address conflict) give real-time bus health—no logic analyzer required during commissioning.

Environmental qualification meets –20 °C to +70 °C operation and 95 % RH non-condensing, permitting installation in turbine auxiliaries or control rooms with minimal HVAC. CE certification simplifies European project approvals.

GE DS3800HACA1A1A

DS3800HACA1A1A: Technical Specifications

-

Model Number: DS3800HACA1A1A

-

Manufacturer: General Electric (GE Energy)

-

Product Type: Card Address Board (Address Decoder)

-

System Compatibility: Speedtronic Mark IV (daughterboard slot)

-

Function: Address decoding, chip-select generation, bus isolation

-

Address Width: 20-bit decode, 4 kB to 64 kB block selectable

-

Control Lines: Read, write, chip-enable, wait-state (jumper-selectable)

-

Isolation: 1500 V AC channel-to-ground, 500 V channel-to-channel

-

Jumpers: 30 (address decode, chip-select, wait-state)

-

Connectors: 2 × 20-pin ribbon, keyed, gold-plated

-

Propagation Delay: <15 ns decode-to-select, <5 ns skew between lines

-

Surge Protection: >500 V TVS on every pin, <1 ns response

-

Power Rails: +5 V DC logic, <0.3 W total

-

LEDs: Green = decode active, Red = address conflict / parity error

-

Temp Range: -20 °C to +70 °C operational, -40 °C to +85 °C storage

-

Humidity: 95 % RH non-condensing

-

Certifications: CE, RoHS, Mark IV form-factor compliant

Core Features & Customer Value

Deterministic Address Decoding for TMR Voting

<15 ns propagation and <5 ns skew ensure bit-exact congruence across three CPU legs; voter disagreement is <1 ns, mandatory for SIL2 TMR certification and grid-code compliance.

<15 ns propagation and <5 ns skew ensure bit-exact congruence across three CPU legs; voter disagreement is <1 ns, mandatory for SIL2 TMR certification and grid-code compliance.

Hot-Swappable in TMR Strings

Redundant Mark IV allows online replacement of one address card; remaining two legs continue voting. MTTR is <5 min—no outage, no load shed, no restart required.

Redundant Mark IV allows online replacement of one address card; remaining two legs continue voting. MTTR is <5 min—no outage, no load shed, no restart required.

Field-Configurable Without Software

30 jumpers map I/O addresses, chip-select enables, and wait-state insertion—technician can re-purpose for different daughterboards using only a tweaker and the silk-screen legend, eliminating OEM software dependency.

30 jumpers map I/O addresses, chip-select enables, and wait-state insertion—technician can re-purpose for different daughterboards using only a tweaker and the silk-screen legend, eliminating OEM software dependency.

Surge-Hardened for Turbine Deck

TVS diodes clamp >500 V spikes from servo drives, contactors, or lightning. 1500 V isolation prevents ground-fault propagation to CPU cards, reducing unplanned replacement by >60 % compared with non-isolated decoders.

TVS diodes clamp >500 V spikes from servo drives, contactors, or lightning. 1500 V isolation prevents ground-fault propagation to CPU cards, reducing unplanned replacement by >60 % compared with non-isolated decoders.

GE DS3800HACA1A1A

Typical Applications

Gas Turbine CPU-to-I/O Bridge

Primary decoder for Frame 7/9 Mark IV racks: maps CPU address space to servo amplifiers, pulse-rate inputs, and sequencer relays. Deterministic timing guarantees bit-exact voting during start-up, load ramps, and emergency trips.

Primary decoder for Frame 7/9 Mark IV racks: maps CPU address space to servo amplifiers, pulse-rate inputs, and sequencer relays. Deterministic timing guarantees bit-exact voting during start-up, load ramps, and emergency trips.

Steam Turbine Governor & Protection I/O

Decodes governor servo, vibration monitor, and trip solenoid addresses in steam turbine Mark IV retrofits. Wait-state jumpers slow bus cycle to match slower servo amplifiers, preventing data corruption during transients.

Decodes governor servo, vibration monitor, and trip solenoid addresses in steam turbine Mark IV retrofits. Wait-state jumpers slow bus cycle to match slower servo amplifiers, preventing data corruption during transients.

Black-Start & Emergency Sequencing

Maps emergency battery charger, diesel starter, and breaker-close I/O into CPU memory space during island-mode black-start. Fail-safe decoder defaults to disabled on loss of 5 V, meeting IEC 61508 SIL2 requirements.

Maps emergency battery charger, diesel starter, and breaker-close I/O into CPU memory space during island-mode black-start. Fail-safe decoder defaults to disabled on loss of 5 V, meeting IEC 61508 SIL2 requirements.